2013年09月11日

DDSによる fractional N PLL

DDSを信号源として用いるには,いくつか課題がある.

100MHz以上の高いクロック周波数で動作するDDSの入手が容易になり,安定で高い周波数を発生させることが簡単にできるようになったが,その際,DDSのクロックの信号源が問題となる.

100MHz超える信号を出力可能な発振器の多くは内部がPLLであり,出力信号はジッタが多くそのままでは十分なC/Nが得られない.

100MHz以上でC/Nのよい信号を得るには,例えば,オーバートーン水晶発振回路やてい倍回路を準備する必要がある.

また,スプリアスの問題がある.

DDSの場合,高調波以外のスプリアスも多く存在するため,LCフィルタでは除去しきれない可能性がある.そのため,PLLと組み合わせるケースがよくみられる.

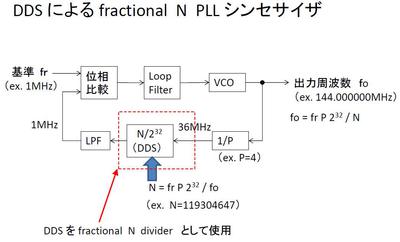

PLLと組み合わせるのであれば,DDSをfractional N divider としたPLLシンセサイザ

(http://www.analog.com/static/imported-files/jp/data_sheets/AD9851_JP.pdf の図5)

とすれば,クロック信号源の問題は解決する.

図のように,DDSのクロックとしてVCOの出力信号(あるいはVCOの出力信号をプリスケーラで1/Pに分周したもの)を入力する.よって,高い周波数のクロック信号源を別に作る必要がない.

基準信号は,この例では1MHzとしている.この程度の周波数であれば,簡単な水晶発振でC/Nのよい信号が容易に作れる.

また,DDSの出力信号の最大周波数は,実用的にはクロックの1/3程度(理論的には1/2)であるが,

この構成であればDDSの最大クロック周波数以上の信号が得られるという利点がある.

つまり,最大クロック周波数が低めの安価なDDSが活用できることになる.さらにプリスケーラ次第でいくらでも高い周波数が得られる.

一般的なPLLシンセサイザと異なるのは,周波数が設定値Nに逆比例するということのみである.

100MHz以上の高いクロック周波数で動作するDDSの入手が容易になり,安定で高い周波数を発生させることが簡単にできるようになったが,その際,DDSのクロックの信号源が問題となる.

100MHz超える信号を出力可能な発振器の多くは内部がPLLであり,出力信号はジッタが多くそのままでは十分なC/Nが得られない.

100MHz以上でC/Nのよい信号を得るには,例えば,オーバートーン水晶発振回路やてい倍回路を準備する必要がある.

また,スプリアスの問題がある.

DDSの場合,高調波以外のスプリアスも多く存在するため,LCフィルタでは除去しきれない可能性がある.そのため,PLLと組み合わせるケースがよくみられる.

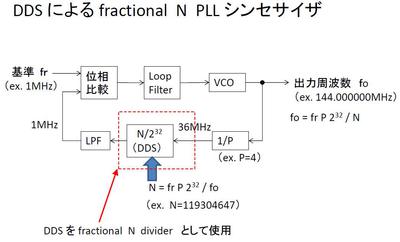

PLLと組み合わせるのであれば,DDSをfractional N divider としたPLLシンセサイザ

(http://www.analog.com/static/imported-files/jp/data_sheets/AD9851_JP.pdf の図5)

とすれば,クロック信号源の問題は解決する.

図のように,DDSのクロックとしてVCOの出力信号(あるいはVCOの出力信号をプリスケーラで1/Pに分周したもの)を入力する.よって,高い周波数のクロック信号源を別に作る必要がない.

基準信号は,この例では1MHzとしている.この程度の周波数であれば,簡単な水晶発振でC/Nのよい信号が容易に作れる.

また,DDSの出力信号の最大周波数は,実用的にはクロックの1/3程度(理論的には1/2)であるが,

この構成であればDDSの最大クロック周波数以上の信号が得られるという利点がある.

つまり,最大クロック周波数が低めの安価なDDSが活用できることになる.さらにプリスケーラ次第でいくらでも高い周波数が得られる.

一般的なPLLシンセサイザと異なるのは,周波数が設定値Nに逆比例するということのみである.

Posted by Tetsuji at 21:02│Comments(0)